1. コプラナリティとは?

コプラナリティ(Coplanarity)とは、電子部品(コネクタ)の端子やBGAのはんだボールが同一平面上にあるかどうかを示す指標です。特にリフロー実装においては、部品の接合面が基板と均一に接触していることが求められます。コプラナリティが確保されていない場合、接合不良や電気的特性の低下を招く可能性があります。

2. コプラナリティの影響

コプラナリティが確保されていない場合、以下のような問題が発生する可能性があります。

2-1. はんだ接合不良

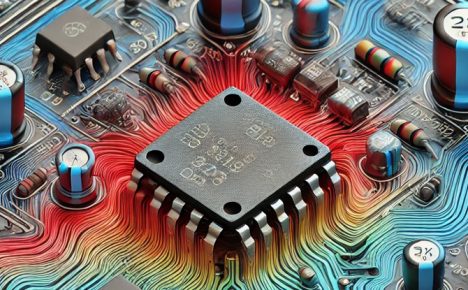

リフロー工程では、はんだペーストが溶融して部品端子と基板パッドを接合します。しかし、部品のコプラナリティが悪い(平坦では無い状態)と、一部の端子が基板パッドに接触せず、オープン接合(未接続)やブリッジ(隣接端子間のショート)が発生するリスクが高まります。

2-2. 電気的特性の低下

特に高周波回路や高速信号伝送を行う製品では、接合不良が電気的特性に大きな影響を与えます。接触不良によるインピーダンス変動や信号反射が発生し、製品の性能低下につながることがあります。

2-3. 機械的信頼性の低下

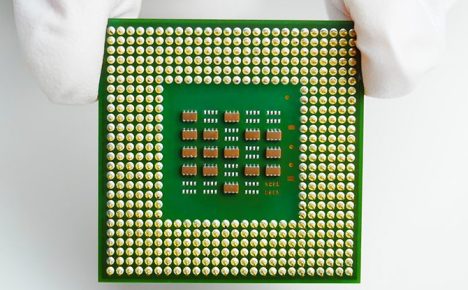

コプラナリティが悪い部品は、温度サイクルや振動試験時にストレスが集中しやすく、クラックや破損の原因となります。特にBGAやQFNなどのパッケージでは、はんだ接合部の信頼性に直接関わるため、注意が必要です。

3. コプラナリティを阻害する課題

コプラナリティを阻害する課題としては以下のような事項が上げられます。

3-1. 部品製造精度の問題

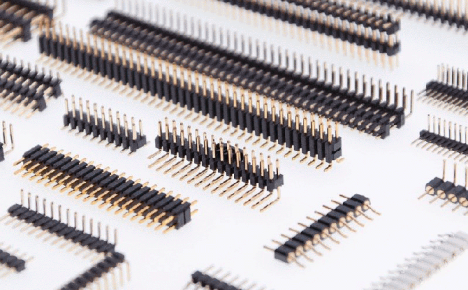

電子部品メーカーの製造工程において、リードやボールの高さにばらつきが生じることがあります。このばらつきがコプラナリティ不良の原因となるため、高精度な製造管理が求められます。

3-2. 基板設計の影響

基板の反りやねじれもコプラナリティに影響を与えます。特に、大型基板や多層基板では、リフロー加熱時の熱膨張によって変形が発生しやすく、部品の平面性が損なわれるリスクがあります。

3-3. 実装プロセスの影響

はんだペーストの印刷精度やリフロー加熱プロファイルもコプラナリティに影響します。はんだ量が不足していると接合強度が低下し、過剰な場合はブリッジが発生しやすくなります。

4. コプラナリティ不良を防ぐための対策

これまでコプラナリティが与える影響や阻害する課題をご紹介しましたが、コプラナリティ不良を防ぐための対策としては以下のような事項が考えれます。

4-1. 高精度な部品選定

信頼性の高いメーカーの電子部品を使用し、部品のコプラナリティ仕様を事前に確認することが重要です。また、実装前に光学検査やX線検査を行い、不良部品の選別を行うことも効果的です。

4-2. 基板設計の最適化

基板の反りやねじれを最小限に抑えるために、適切な基板材質を選定し、配線設計のバランスを考慮することが重要です。また、大型基板では補強リブやスティフナーを追加することで変形を防ぐことができます。

4-3. 実装プロセスの最適化

■はんだペーストの管理

印刷厚みの均一化や、適切な粘度のはんだペーストを使用する。

■リフロー加熱プロファイルの調整

急激な温度変化を避け、均一な熱分布を確保する。

■事前検査の強化

リフロシミュレータなど装置を活用し、どの温度でどの位コプラナリティが悪化するか、現状を正しく理解して実装不良を未然に防ぐ。

4-4. はんだ接合強度の向上

微細ピッチ部品では、はんだ合金の選定やフラックス成分の最適化が接合信頼性の向上に寄与します。また、窒素リフローを採用することで、酸化を防ぎ、より安定した接合を実現できます。

5. まとめ

コプラナリティは、リフロー実装の品質を左右する重要な要素です。適切な部品選定、基板設計、実装プロセスの管理を行うことで、接合不良や電気的特性の劣化を防ぐことができます。特に、BGAやQFNといったリードレスパッケージでは、わずかな高さのズレが製品寿命や信頼性に影響を与えるため、慎重な対策が必要です。今後も電子機器の高密度化が進む中で、コプラナリティ管理の重要性はますます高まるでしょう。本記事の内容を参考に、リフロー実装の品質向上に取り組んでください。